5CEFA7F31I7N täze we özboluşly ic çipleri integrirlenen zynjyrlar elektron komponentleri BOM hyzmatyny satyn almak üçin iň gowy baha

Önüm aýratynlyklary

| TYPE | Düşündiriş |

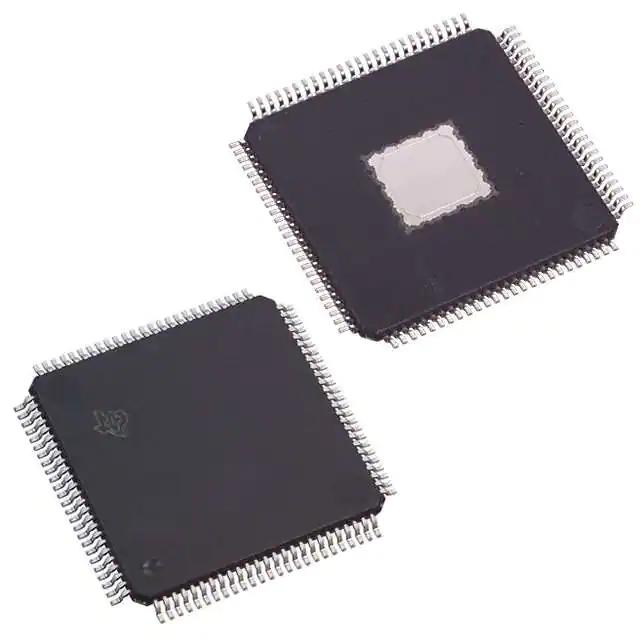

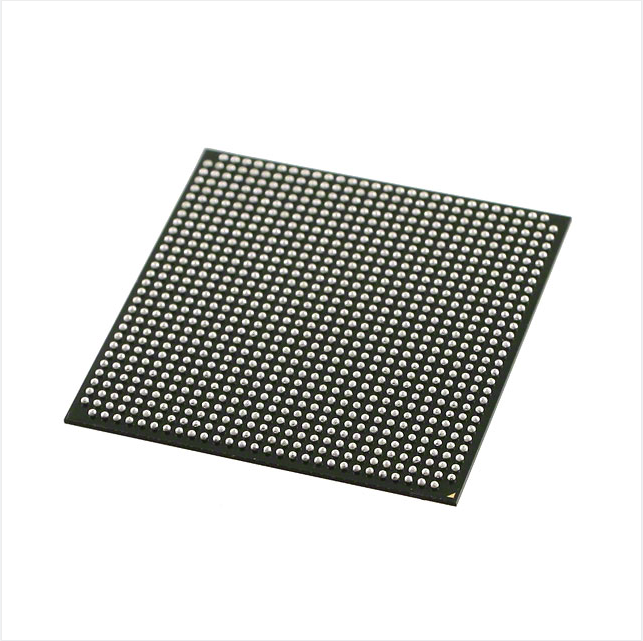

| Kategoriýa | Toplumlaýyn zynjyrlar (IC) |

| Mfr | Intel |

| Seriýa | Siklon® VE |

| Bukja | Gatnaşyk |

| Standart paket | 27 |

| Önümiň ýagdaýy | Işjeň |

| LAB / CLB-leriň sany | 56480 |

| Logiki elementleriň / öýjükleriň sany | 149500 |

| Jemi RAM bitleri | 7880704 |

| I / O sany | 480 |

| Naprýa .eniýe - üpjünçilik | 1.07V ~ 1.13V |

| Gurnama görnüşi | Faceerüsti dag |

| Işleýiş temperaturasy | -40 ° C ~ 100 ° C (TJ) |

| Bukja / gap | 896-BGA |

| Üpjün ediji enjam bukjasy | 896-FBGA (31 × 31) |

| Esasy önümiň belgisi | 5CEFA7 |

1. performanceokary öndürijilik üçin Wirtex seriýasy FPGA

“Virtex” seriýasy Xilinx-iň ýokary derejeli önümi we bu pudakda iň ýokary önümdir.Xilinx, Virtex seriýaly önümleri bilen bazarda ýeňiş gazandy we şeýlelik bilen FPGA-nyň öňdebaryjy üpjünçisi hökmünde orny eýeledi.Xilinx, FPGA önümleriniň Wirtex maşgalasy bilen meýdan programmirläp boljak derwezäniň massiw pudagyna ýolbaşçylyk edýär diýmek bolar.Esasan telekom infrastrukturasy, awtoulag pudagy we ýokary derejeli sarp ediş elektronikasy ýaly programmalara gönükdirilendir.Häzirki akym çiplerine Witrex-2, Virtex-2 Pro, Virtex-4, Virtex-5, Virtex-6 we Virtex-7 kategoriýalary girýär.

“Virtex-2” seriýasy 2002-nji ýylda 0,15nm prosess, 1.5V ýadro naprýa .eniýesi, 420MHz çenli iş sagady, 20-den gowrak I / O interfeýs standartlaryny goldamak, ulgamyň doly sagadyny dolandyrmak mümkinçilikleri we içerki IP ýadrosy bilen girizildi. Wirtex seriýasyna garanyňda has köp çeşme we has ýokary öndürijilikli çipiň islendik ýerinde bellemäge mümkinçilik berýän esasy tehnologiýa.Virtex maşgalasyndan has ýokary öndürijilik.

“Virtex-2 Pro” seriýasy güýçlendirilen gaýtadan işlemek mümkinçilikleri we oturdylan PowerPC405 ýadrosy bilen “Virtex-2” -e esaslanýar we ýokary tizlikli goşmaça goşmaça ýokary öndürijilikli ulgamlaryň ýüzbe-ýüz bolýan kynçylyklaryny çözmek üçin ösen “Active Interconnect” tehnologiýasyny öz içine alýar. Gigabit Ethernet çözgütlerini üpjün etmek üçin yzygiderli geçiriji.

“Virtex-4” maşgalasy, “Silikon Blok kombinasiýa moduly” (ASMBL) arhitekturasyna esaslanýar, sagat ýygylygy 500 MGs-a çenli ýokary logiki dykyzlygy görkezýär;DCM modullary, PMCD faza gabat gelýän sagat bölüjileri, çipdäki diferensial sagat torlary bilen;Integrirlenen FIFO dolandyryş logikasy bilen 500 MGts SmartRAM tehnologiýasy we her I / O 1 Gbps I / O we Xtreme DSP logiki çipi üçin ChipSync çeşmesini sinhronizasiýa tehnologiýasy bilen birleşdirildi.Dizaýnerler, zerurlyklaryna görä, logiki köp talap edýän dizaýnlar üçin dürli “Virtex-4” kiçi ulgamlaryny saýlap bilerler: “Virtex-4 LX”, ýokary öndürijilikli signal işleýiş programmalary üçin: “Virtex-4 SX”, ýokary tizlikli seriýa birikmesi we oturdylan gaýtadan işlemek programmalary: Virtex- 4 FX.Wirtex-4 maşgalasy, 2005-nji ýylyň ahyryndan bäri köpçülikleýin önümçilige başlan WirtexII seriýasyndaky ähli ölçeglerde ep-esli gowulaşma hödürleýär, VirtexII, VirtexII-Pro çalyşdy we Xilinx-iň häzirki iň ýokary önümidir - FPGA bazaryny satmak.

“Virtex-5” maşgalasy häzirki zaman 65nm mis gaýtadan işlemek tehnologiýasyna esaslanýar we bäş aýratyn platforma (kiçi maşgala) öz içine alýan ikinji nesil ASMBL (Advanced Silikon Building Blok) sütün arhitekturasyny ulanýar.Her platforma köp ösen logiki dizaýnlaryň isleglerini kanagatlandyrmak üçin dürli aýratynlyk derejelerini öz içine alýar.Döwrebap ýokary öndürijilikli logika arhitekturasyndan başga-da, Wirtex-5 FPGA-larda gaty gaty IP ulgamy derejeli modullar bar, şol sanda güýçli 36 Kb Blok RAM / FIFO, ikinji nesil 25 × 18 DSP dilim, içerki CNC impedansy bilen SelectIO tehnologiýasy, ChipSync çeşmesini sinhronlaşdyrma interfeýs modullary, ulgam gözegçiliginiň işleýşi we integrirlenen DCM (Sanly sagat dolandyryjysy) we PLL (Faza Locked Loop) sagat generatorlary we ösen konfigurasiýa opsiýalary.Platforma esasly beýleki aýratynlyklar, güýçlendirilen seriýa birikmesi üçin güýç bilen optimallaşdyrylan ýokary tizlikli seriýa geçiriji moduly, PCI Express bilen utgaşdyrylan ahyrky nokat moduly, üç döwletli Ethernet MAC (mediýa giriş gözegçiligi) we ýokary öndürijilikli PowerPC 440 mikroprosessor öz içine alýar. ösen logika dizaýnerlerine, FPGA esasly ulgamlarynda iň ýokary öndürijilik derejesini görkezmäge mümkinçilik berýän içerki modul.

“Virtex-6” maşgalasy FPGA bazaryna iň täze, iň ösen aýratynlyklary hödürleýär.“Virtex-6 FPGAs”, ösüş tagallalary başlansoň dizaýnerlere innowasiýa ünsi jemlemek üçin enjam we programma üpjünçiliginiň böleklerini üpjün edýän maksatly synag krowatlary üçin programmirläp bolýan kremniy tehnologiýa binýadydyr.“Virtex-6” maşgalasynda birnäçe dürli kiçi maşgalalary öz içine alýan üçünji nesil ASMBL (ösen kremniy portfel moduly) sütün arhitekturasy bar.Bu syn, LXT, SXT we HXT kiçi maşgaladaky enjamlary suratlandyrýar.Her bir maşgalada ösen logiki dizaýn talaplarynyň giň toplumyny netijeli kanagatlandyrmak üçin dürli aýratynlyklar bar.“Virtex-6 FPGA” ýokary öndürijilikli logiki matadan başga-da, içerki ulgam derejesindäki birnäçe modullary öz içine alýar.Bu aýratynlyklar logiki dizaýnerlere FPGA ulgamlarynda iň ýokary öndürijilik we işleýiş derejesini gurmaga mümkinçilik berýär.“Virtex-6 FPGAs” ýokary öndürijilikli logika dizaýnerleriniň, ýokary öndürijilikli DSP dizaýnerleriniň we ýokary öndürijilikli içerki ulgam dizaýnerleriniň isleglerini kanagatlandyrmak üçin iň oňat çözgüt hödürleýär, görlüp-eşidilmedik logika, DSP, birikme we ýumşak mikroprosessor mümkinçiliklerini getirýär.

“Virtex-7”, 2011-nji ýylda 28nm prosessde hödürlenen, ýokary derejeli FPGA önümidir, bu müşderilere öndürijiligi we kuwwaty ýokarlandyrmak bilen çykdajylary we güýji sarp etmegi azaldýan aýratynlyklary aýyrmak we aýyrmak erkinligini berýär, şeýlelik bilen ösüşi peseltmek we ýerleşdirmek üçin maýa goýumlaryny azaldýar. -kost we ýokary öndürijilikli maşgalalar.Mundan başga-da, “Wirtex-6” bilen deňeşdirilende 35 göterim arzanladyş, artdyrylan konwersiýa ýa-da in engineeringenerçilik maýa goýumlary bilen öndürijiligi hasam ýokarlandyrýar.

.png)