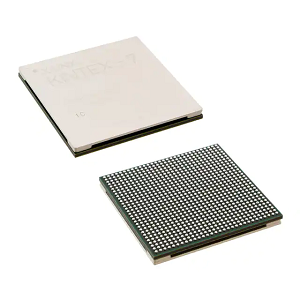

XC7K420T-2FFG901I - Toplumlaýyn zynjyrlar, oturdylan, meýdan programmirläp boljak derweze massiwleri

Önüm aýratynlyklary

| TYPE | ILLUSTRATE |

| kategoriýasy | Toplumlaýyn zynjyrlar (IC)Içerki Meýdanyň programmirläp boljak derweze massiwleri (FPGAs) |

| öndüriji | AMD |

| seriýasy | Kintex®-7 |

| örtmek | tarelka |

| Haryt ýagdaýy | Işjeň |

| DigiKey programmirläp bolýar | Barlanmady |

| LAB / CLB belgisi | 32575 |

| Logika elementleriniň / birlikleriniň sany | 416960 |

| RAM bitleriniň umumy sany | 30781440 |

| I / Os sany | 380 |

| Naprýa .eniýe - Elektrik üpjünçiligi | 0.97V ~ 1.03V |

| Gurnama görnüşi | Faceerüsti ýelim görnüşi |

| Işleýiş temperaturasy | -40 ° C ~ 100 ° C (TJ) |

| Bukja / ýaşaýyş jaýy | 900-BBGA 、 FCBGA |

| Satyjy komponentiniň bukulmagy | 901-FCBGA (31x31) |

| Önümiň baş belgisi | XC7K420 |

| TYPE | ILLUSTRATE |

| kategoriýasy | Toplumlaýyn zynjyrlar (IC)Içerki |

| öndüriji | AMD |

| seriýasy | Kintex®-7 |

| örtmek | tarelka |

| Haryt ýagdaýy | Işjeň |

| DigiKey programmirläp bolýar | Barlanmady |

| LAB / CLB belgisi | 32575 |

| Logika elementleriniň / birlikleriniň sany | 416960 |

| RAM bitleriniň umumy sany | 30781440 |

| I / Os sany | 380 |

| Naprýa .eniýe - Elektrik üpjünçiligi | 0.97V ~ 1.03V |

| Gurnama görnüşi | Faceerüsti ýelim görnüşi |

| Işleýiş temperaturasy | -40 ° C ~ 100 ° C (TJ) |

| Bukja / ýaşaýyş jaýy | 900-BBGA 、 FCBGA |

| Satyjy komponentiniň bukulmagy | 901-FCBGA (31x31) |

| Önümiň baş belgisi | XC7K420 |

FPGAs

Üstünlikleri

FPGA-laryň artykmaçlyklary aşakdakylar:

.

(2) FPGA-lar ýönekeý derwezäniň zynjyrlaryndan FIR ýa-da FFT zynjyrlaryna çenli blok diagrammalaryny ýa-da Verilog HDL ulanyp döredilip bilner.

(3) FPGA-lary çäksiz gaýtadan programmirläp bolýar, täze dizaýn çözgüdini birnäçe ýüz millisekuntda ýükläp, enjamyň üstünden azaltmak üçin konfigurasiýa ulanyp.

(4) FPGA-nyň işleýiş ýygylygy FPGA çipi we dizaýny bilen kesgitlenýär we käbir talaplary kanagatlandyrmak üçin has çalt çip bilen üýtgedilip ýa-da çalşyrylyp bilner (elbetde, iş ýygylygy çäksiz däl we mümkin ýokarlandyrylmaly, ýöne häzirki IC prosesleri we beýleki faktorlar bilen dolandyrylýar).

Adetmezçilikleri

FPGA-laryň kemçilikleri aşakdakylar:

(1) FPGA-lar ähli funksiýalar üçin apparat üpjünçiligine bil baglaýarlar we şertli böküşler ýaly şahalary ýerine ýetirip bilmeýärler.

(2) FPGA-lar diňe kesgitlenen nokat amallaryny amala aşyryp bilerler.

Gysgaça aýdanyňda: FPGA-lar ähli funksiýalary ýerine ýetirmek üçin enjamlara bil baglaýarlar we tizlik nukdaýnazaryndan aýratyn çipler bilen deňeşdirilip bilner, ýöne umumy maksatly prosessorlar bilen deňeşdirilende dizaýn çeýeliginde uly boşluk bar.

Dilleri we platformalary dizaýn ediň

Programmirläp boljak logiki enjamlar, EDA tehnologiýasy arkaly elektron programmalaryň kesgitlenen funksiýalaryny we tehniki aýratynlyklaryny kesgitleýän apparat göterijileridir.FPGA-lar, bu ýoly amala aşyrýan esasy enjamlaryň biri hökmünde gönüden-göni ulanyja gönükdirilen, aşa çeýe we köp taraply, ulanmak aňsat we enjamda synagdan geçirmäge we durmuşa geçirmäge çalt.

Enjamlaryň beýany dili (HDL) sanly logika ulgamlaryny dizaýn etmek we sanly zynjyrlary suratlandyrmak üçin ulanylýan dil, köplenç ulanylýan esasylary VHDL, Verilog HDL, System Verilog we System C.

Hardwarehli taraplaýyn enjam düşündiriş dili hökmünde, Örän ýokary tizlikli integrirlenen zynjyr enjamlarynyň beýany dili (VHDL), belli bir enjam zynjyryndan garaşsyz we dizaýn platformasyndan garaşsyz, giň gerimli düşündiriş ukybynyň artykmaçlyklary bilen däl belli enjamlara bagly we çylşyrymly dolandyryş logikasynyň dizaýnyny berk we gysga kodda we ş.m. beýan etmek ukybyna baglydyr. Köp EDA kompaniýalary tarapyndan goldanýar we elektron dizaýn pudagynda giňden ulanylýar.giňden ulanylýar.

VHDL zynjyr dizaýny üçin ýokary derejeli dil bolup, beýleki enjam düşündiriş dilleri bilen deňeşdirilende, ýönekeý dil, çeýeligi we enjam dizaýnyndan garaşsyzlygy, ony EDA tehnologiýasy üçin umumy apparat beýany diline öwürýär we EDA tehnologiýasyny has köp edýär. dizaýnerler üçin elýeterli.

Verilog HDL, modellemek, sintez we simulýasiýa ýaly enjamlary dizaýn prosesiniň birnäçe tapgyrynda ulanylyp bilinýän giňden ulanylýan apparat düşündiriş dili.

Verilog HDL artykmaçlyklary: C-e meňzeş, öwrenmek aňsat we çeýe.Ýagdaýa bagly.Gyjyndyryjy we modelirlemegiň artykmaçlyklary.Adetmezçilikleri: düzülen wagtynda köp ýalňyşlygy tapyp bolmaýar.

VHDL Pros: Gaty sintaksis, aýdyň iýerarhiýa.Adetmezçilikleri: uzak tanyşlyk wagty, ýeterlik çeýe däl.

Quartus_II programma üpjünçiligi, dürli FPGA we CPLD-leriň dizaýn zerurlyklaryny kanagatlandyryp bilýän we çip programmirläp bolýan ulgam dizaýny üçin giňişleýin gurşaw bolan Altera tarapyndan işlenip düzülen doly platformaly dizaýn gurşawydyr.

Vivado Design Suite, FPGA satyjysy Xilinx tarapyndan 2012-nji ýylda çykarylan toplumlaýyn dizaýn gurşawy. Bu ýokary integrirlenen dizaýn gurşawyny we ulgamdan IC derejesine çenli gurallaryň täze neslini öz içine alýar, bularyň hemmesi umumy göwrümli maglumat modeline we umumy düzediş gurşawyna esaslanýar.“Xilinx Vivado Design Suite” dizaýnlara aňsatlyk bilen ulanyp boljak FIFO IP ýadrosyny üpjün edýär.